Comparison of DDR4 and DDR5 SODIMM DRAM modules by APACER

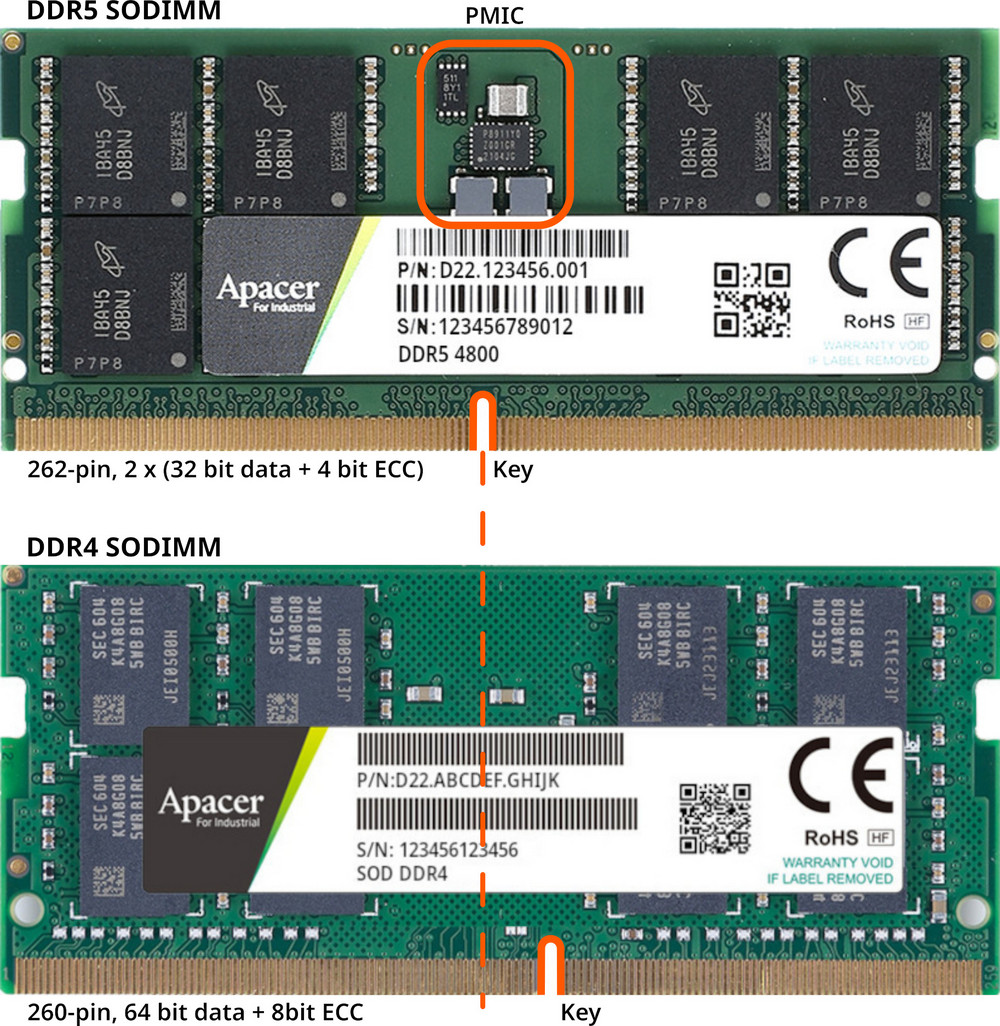

Form factor comparison

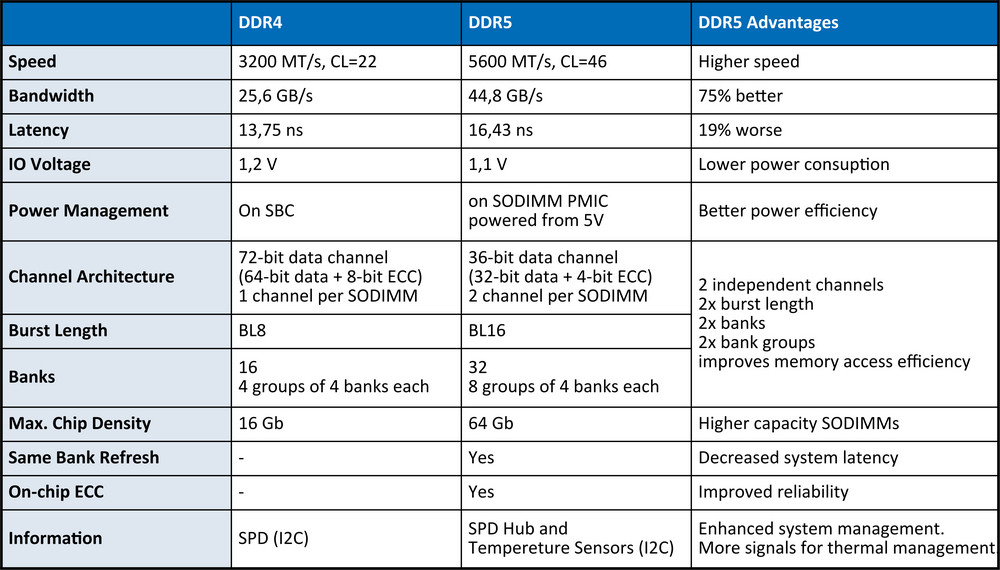

Bandwidth and memory latency

Calculation based on simplified equations, Bandwidth = Speed [MT/s]*8/1000, Memory latency[ns] = 2000/Speed[MT/s] leads to the conclusion that DDR5600 CL46 has 75% more bandwidth and 19% worse latency than DDR4 3200 CL22.

However, according to tests made by Anandtech, DDR5-4800 CL40 memory increases system latency to 92,8 ns compared to 90 ns with DDR4-3200 CL22. This is only ~3% more, which is visible in synthetic benchmarking but virtually unnoticeable in most real-world use cases. The similar results can be expected also for DDR5 5600 CL46 memory.

Higher DRAM module capacity

DDR4 maximum memory density is 16 Gb per chip, so with 16 chips, this translates to 256 Gbit or a total of 32 GB. DDR5, in comparison, has 64 Gb per chip, translating to 1024 Gbit or a total of 128 GB – 4X larger capacity than DDR4.

On-chip ECC

Smaller memory cells, required for higher capacity, along with higher clock frequency, increase the probability of single-bit errors on the DRAM chip. The DDR5 DRAM chip calculates the ECC for the data being written and stores the ECC on the same chip. In a DRAM read operation, the chip reads the current data and ECC and can correct any single-bit error on any of the read data bits.

The classic SODIMM DDR5 ECC memory module uses an additional chip where ECC and two 36-bit channels (32-bits for data + 4-bits for ECC) are stored. The memory controller calculates the ECC for the data to be written and then writes the data and ECC to the memory module. During a read operation, the controller reads the data and ECC and generates the ECC for the read data. If the calculated and loaded ECC are the same, the data is sent to the CPU, otherwise the data is sent to the error correction program. Thus, data is protected all the way between the memory controller and the memory chip.

Improved efficiency of access to memory

Channel architecture

Two independent 32-bit channels allow better optimization of memory access.

2x burst length, 2 independent 32-bit channels

A burst length of 16 (BL16) allows a single burst to access 64 bytes of data, a typical CPU buffer line size, from a single channel of a DDR5 DRAM module. This means that a DDR5 5600 DRAM module can perform seven 64-byte operations at the same time it takes a DDR4 3200 to perform four operations.

2x number of banks

DDR5 doubles the number of bank groups to 8 while keeping the number of banks per bank group the same, 4. Access to different bank groups take is faster compared to bank accesses within the same bank group.

Same bank refresh

In DDR4, all memory banks must be refreshed simultaneously, even if only one of the 16 memory banks on a DIMM needs to be refreshed, so the CPU must wait for the refresh to complete and cannot access the memory. In DDR5, the “same bank refresh” feature allows refreshing one bank in the group instead of all banks. This means that three banks out of four remain available to the CPU.

Apacer DDR5 SODIMM memory modules can be found in our range as stock products available immediately for your projects.

Your feedback helps us create truly useful content for our readers. Appreciate the above information with an imaginary contribution for this article.

If you have any questions or comments, please don't hesitate to contact us. Thanks again for your time and trust.

Are you interested in more information about Apacer products or technical advice when choosing a product? Or do you have another question or request? Please fill out the following form; we are happy to help.

Do you like our articles? Do not miss any of them! You do not have to worry about anything, we will arrange delivery to you.